- 您现在的位置:买卖IC网 > Sheet目录3872 > PIC18F4450T-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX16 44QFN

209

XMEGA A [MANUAL]

8077I–AVR–11/2012

A high-to-low transition on the SCL line will force the line low for all masters on the bus, and they will start timing their low

clock period. The timing length of the low clock period can vary among the masters. When a master (DEVICE1 in this

case) has completed its low period, it releases the SCL line. However, the SCL line will not go high until all masters have

released it. Consequently, the SCL line will be held low by the device with the longest low period (DEVICE2). Devices

with shorter low periods must insert a wait state until the clock is released. All masters start their high period when the

SCL line is released by all devices and has gone high. The device which first completes its high period (DEVICE1) forces

the clock line low, and the procedure is then repeated. The result is that the device with the shortest clock period

determines the high period, while the low period of the clock is determined by the device with the longest clock period.

19.4

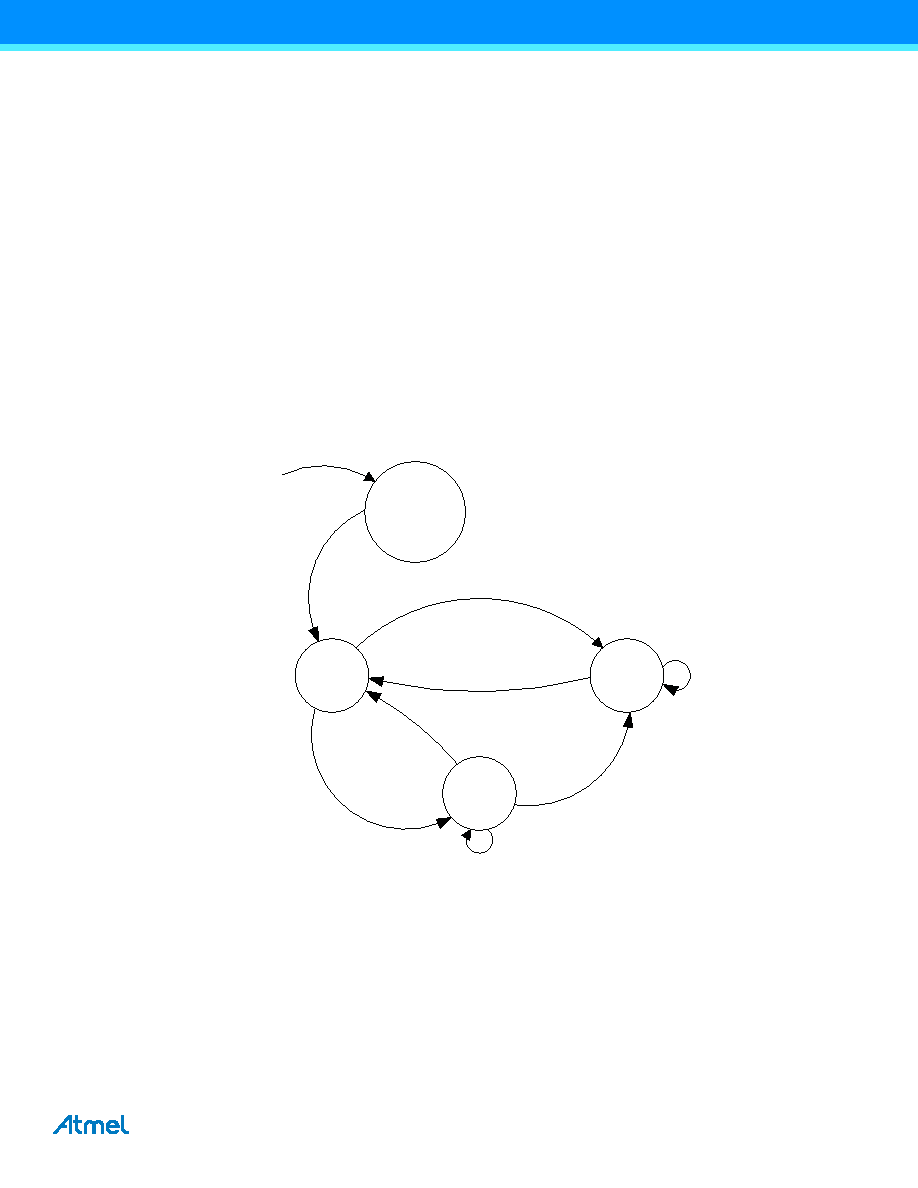

TWI Bus State Logic

The bus state logic continuously monitors the activity on the TWI bus lines when the master is enabled. It continues to

operate in all sleep modes, including power-down.

The bus state logic includes START and STOP condition detectors, collision detection, inactive bus timeout detection,

and a bit counter. Theseare used to determine the bus state. Software can get the current bus state by reading the bus

state bits in the master status register. The bus state can be unknown, idle, busy, or owner, and is determined according

to the state diagram shown in Figure 19-11. The values of the bus state bits according to state are shown in binary in the

figure.

Figure 19-11.Bus state, state diagram.

After a system reset and/or TWI master enable, the bus state is unknown. The bus state machine can be forced to enter

idle by writing to the bus state bits accordingly. If no state is set by application software, the bus state will become idle

when the first STOP condition is detected. If the master inactive bus timeout is enabled, the bus state will change to idle

on the occurrence of a timeout. After a known bus state is established, only a system reset or disabling of the TWI master

will set the state to unknown.

When the bus is idle, it is ready for a new transaction. If a START condition generated externally is detected, the bus

becomes busy until a STOP condition is detected. The STOP condition will change the bus state to idle. If the master

inactive bus timeout is enabled, the bus state will change from busy to idle on the occurrence of a timeout.

If a START condition is generated internally while in idle state, the owner state is entered. If the complete transaction was

performed without interference, i.e., no collisions are detected, the master will issue a STOP condition and the bus state

P + Timeout

Write ADDRESS

IDLE

(0b01)

S

BUSY

(0b11)

UNKNOWN

(0b00)

OWNER

(0b10)

Arbitration

Lost

Command P

Write

ADDRESS(Sr)

Sr

(S)

RESET

P + Timeout

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F4321T-I/ML

IC PIC MCU FLASH 4KX16 44QFN

PIC18F4221T-I/ML

IC PIC MCU FLASH 2KX16 44QFN

PIC18F2321T-I/ML

IC PIC MCU FLASH 4KX16 28QFN

PIC18F2221T-I/SO

IC PIC MCU FLASH 2KX16 28SOIC

PIC16LF1939-I/MV

IC MCU 8BIT 28KB FLASH 40-UQFN

PIC24F16KL402-I/SP

IC MCU 16BIT 16KB FLASH 28-SPDIP

PIC18F24J11-I/SS

IC PIC MCU FLASH 16K 2V 28-SSOP

PIC24F16KA101-I/SO

IC PIC MCU FLASH 16K 20-SOIC

相关代理商/技术参数

PIC18F4450T-I/PT

功能描述:8位微控制器 -MCU 16KB FL 768 RAM 34 I/O FS-USB 2.0 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-BL

制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB 制造商:POWERLITE SYSTEMS 功能描述:PIC18F445 W/ BOOTLOADER, FOR FLASHLAB; Silicon Manufacturer:Powerlite Systems; Core Architecture:PIC; Kit Contents:Board; Features:Bootloader Programming, RS232 Connector for Boot-Loading and Serial Comms ;RoHS Compliant: Yes

PIC18F4455-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/P

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/ML

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4455T-I/PT

功能描述:8位微控制器 -MCU 24kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4458-I/ML

功能描述:8位微控制器 -MCU 24KB Flash 2KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT